设计题目:基于MIPS32的五级流水及中断控制器设计

目录

一、设计实验条件

二、设计任务及要求

三、设计报告的内容

其中,S2-S0 对应的功能表如下:

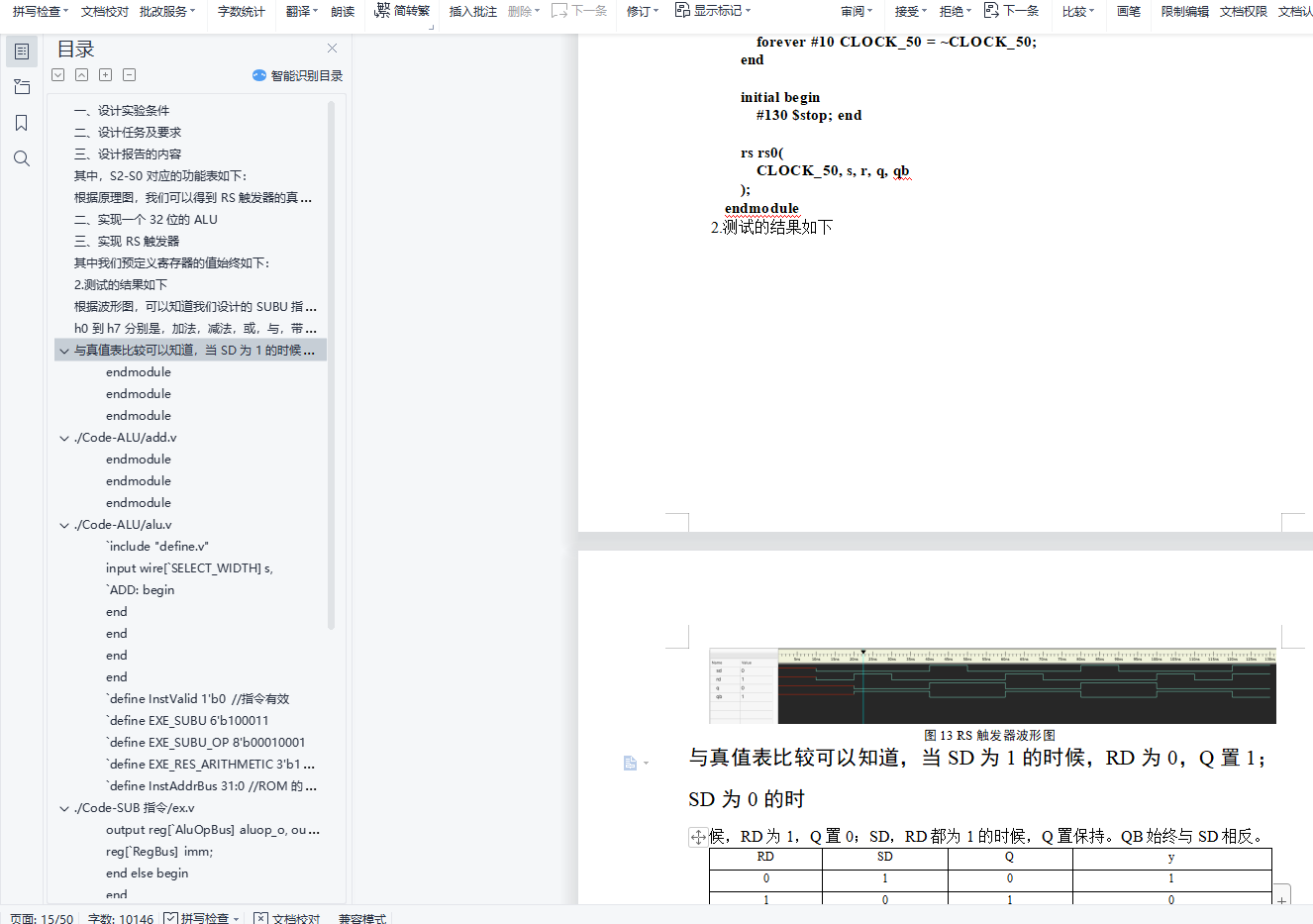

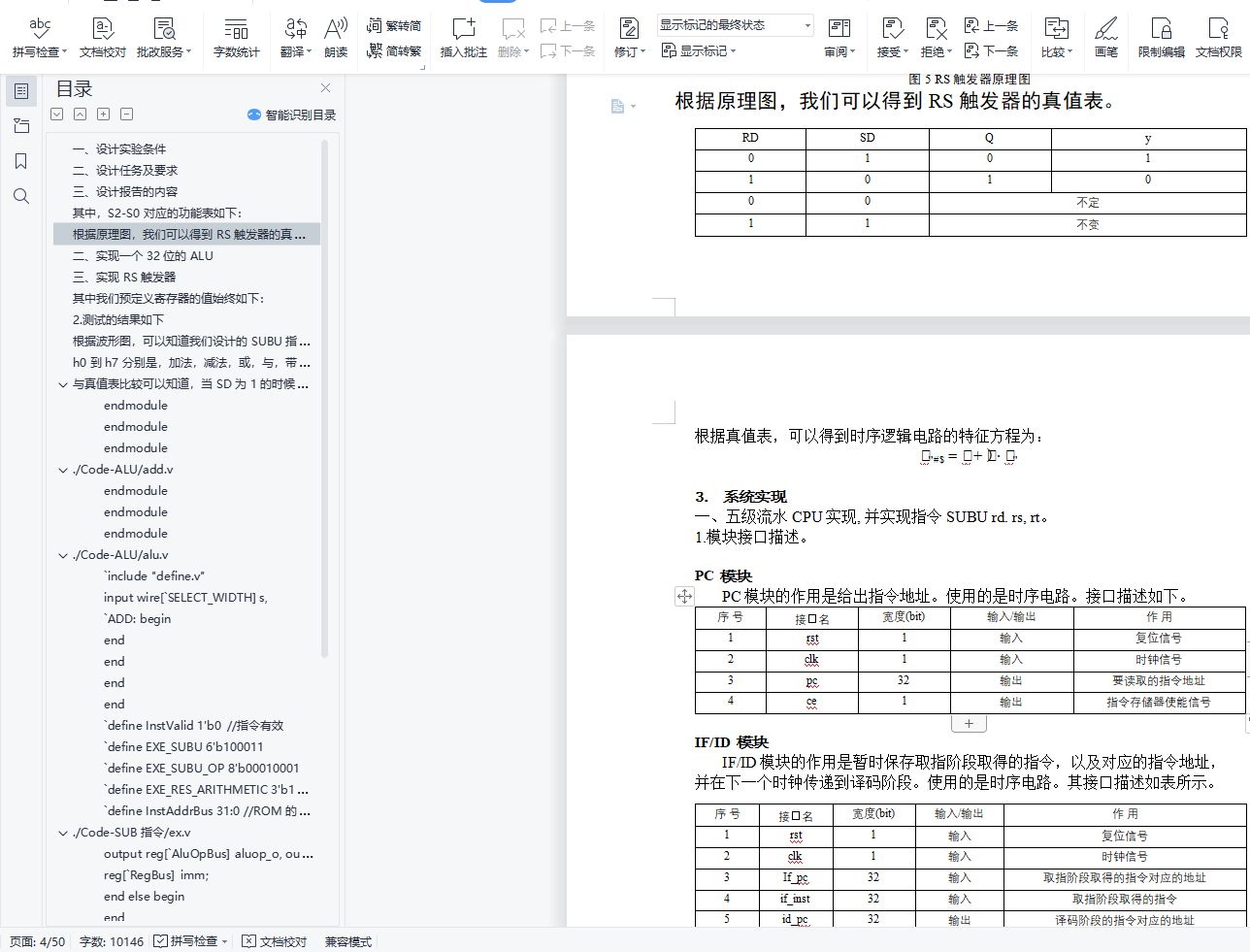

根据原理图,我们可以得到 RS 触发器的真值表。

二、实现一个 32 位的 ALU

三、实现 RS 触发器

其中我们预定义寄存器的值始终如下:

2.测试的结果如下

根据波形图,可以知道我们设计的 SUBU 指令的五级流水是正确的。二 、 32 位 ALU 测 试1.测试的核心代码如下

h0 到 h7 分别是,加法,减法,或,与,带进位的加法和减法,A 取反,以及直接输出 A。比较结果,发现结果没有错误。根据波形图,可以知道我们设计的

与真值表比较可以知道,当 SD 为 1 的时候,RD 为 0,Q 置 1;SD 为 0 的时

endmodule

endmodule

endmodule

./Code-ALU/add.v

endmodule

endmodule

endmodule

./Code-ALU/alu.v

`include "define.v"

input wire[`SELECT_WIDTH] s,

`ADD: begin

end

end

end

end

`define InstValid 1'b0 //指令有效

`define EXE_SUBU 6'b100011

`define EXE_SUBU_OP 8'b00010001

`define EXE_RES_ARITHMETIC 3'b100

`define InstAddrBus 31:0 //ROM 的地址总线宽度

./Code-SUB 指令/ex.v

output reg[`AluOpBus] aluop_o, output reg[`AluSelBus] alusel_o, output reg[`RegBus] reg1_o,

reg[`RegBus] imm;

end else begin

end

end else begin

end

./Code-SUB 指令/id_ex.v

wire[`RegAddrBus] id_wd_o;

wire[`RegBus] ex_reg2_i; wire ex_wreg_i; wire[`RegAddrBus] ex_wd_i;

wire ex_wreg_o; wire[`RegAddrBus] ex_wd_o; wire[`RegBus] ex_wdata_o;

wire mem_wreg_i; wire[`RegAddrBus] mem_wd_i; wire[`RegBus] mem_wdata_i;

wire mem_wreg_o; wire[`RegAddrBus] mem_wd_o; wire[`RegBus] mem_wdata_o;

wire wb_wreg_i; wire[`RegAddrBus] wb_wd_i; wire[`RegBus] wb_wdata_i;

wire reg2_read; wire[`RegBus] reg1_data; wire[`RegBus] reg2_data; wire[`RegAddrBus] reg1_addr; wire[`RegAddrBus] reg2_addr;

./Code-SUB 指令/openmips_min_sopc_tb.v

input wire

input wire[`RegAddrBus] raddr1, output reg[`RegBus] rdata1,

input wire

input wire[`RegAddrBus] raddr2, output reg[`RegBus] rdata2

reg[`RegBus] regs[0:`RegNum-1];

end

`RegNumLog2'h0)) begin

一、设计实验条件

计算机组成原理实验室

二、设计任务及要求

设计并实现指令 SUBU rd. rs, rt;

32 位 ALU;

RS 触发器;

三、设计报告的内容

1. 前言

MIPS 架构 20 多年前由斯坦福大学开发,是一种简洁、优化、具有高度扩展性的 RISC 架构。它的基本特点是:包含大量的寄存器、指令数和字符、可视的管道延时时隙,这些特性使 MIPS 架构能够提供最高的每平方毫米性能和当今 SoC 设计中最低的能耗。

我们知道,RISC 的一大特点是:大量使用寄存器。这是因为寄存器的存取可以在一个时钟周期内完成,同时使用寄存器也大大简化了寻址方式。与其相应 的,MIPS32 的指令中除加载(LDA)和存储(STO)指令外,都是使用寄存器或立即数作为操作数的。MIPS32 中的寄存器分为两类:通用寄存器(General Purpose Register, GPR)、特殊寄存器。

MIPS32 架构定义了 32 个通用寄存器,使用 $0、$1…$31 表示,都是 32 位。其中 $0 般用做常量 0。